Serial Peripheral Interface

Bài viết này cần thêm liên kết tới các bài bách khoa khác để trở thành một phần của bách khoa toàn thư trực tuyến Wikipedia. (tháng 7 2018) |

| Loại | Bus truyền thông nối tiếp đồng bộ | ||

|---|---|---|---|

| Lịch sử | |||

| Người thiết kế | Motorola | ||

| Ngày thiết kế | 1979 | ||

| Dữ liệu | |||

| Giao thức | Truyền thông nối tiếp, Song công | ||

SPI (tiếng Anh: Serial Peripheral Interface, tạm dịch: Giao diện Ngoại vi Nối tiếp) là một chuẩn truyền thông nối tiếp đồng bộ[1] được sử dụng để truyền dữ liệu trong khoảng cách ngắn,[2] thường được sử dụng trong các hệ thống nhúng. SPI được phát triển bởi Motorola vào giữa những năm 1980 và trở thành chuẩn de facto. Các ứng dụng tiêu biểu của SPI có thể kể đến như thẻ nhớ (Secure Digital cards) và giao tiếp màn hình LCD.

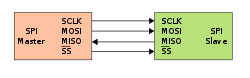

Các thiết bị hỗ trợ SPI giao tiếp ở chế độ chế độ song công toàn phần (full duplex), sử dụng mô hình master - slave với một master trên đường truyền. Thiết bị master khi đó sẽ khởi tạo frame cho việc gởi và nhận. Bus SPI hỗ trợ nhiều slave thông qua việc lựa chọn chân Chip Select (viết tắt: CS, hay còn gọi là Slave select, viết tắt là SS) kết nối từ master đến slave tương ứng với chân CS đó.

Đôi khi SPI cũng còn được gọi là bus nối tiếp bốn dây (four wire serial bus), để phân biệt với các loại bus nối tiếp đã có như three-wire, two-wire và one-wire.

Dù là một chuẩn truyền thông đồng bộ (khi yêu cầu xung clock để đồng bộ tín hiệu trên đường truyền) nhưng SPI khác với giao thức Synchronous Serial Interface (SSI), một giao thức truyền thông nối tiếp đồng bộ cũng sử dụng 4 dây.[3] Giao thức SSI sử dụng dung sai tín hiệu và chỉ cung cấp một kênh truyền đơn hướng trong khi SPI hỗ trợ truyền thông giữa một master và nhiều slave.

Chân tín hiệu[sửa | sửa mã nguồn]

Bus SPI sử dụng 4 chân logic tín hiệu:[4]

- SCLK (Serial Clock): xung clock phát ra từ master

- MOSI (Master Out Slave In): Dành cho việc truyền dữ liệu từ master đến slave. Chân MOSI ở master sẽ kết nối đến chân MOSI ở slave.

- MISO (Master In Slave Out): Dành cho việc truyền dữ liệu từ slave đến master. Chân MISO ở master sẽ kết nối đến chân MISO ở slave.

- CS/SS (Chip/Slave Select): Chân CS được master sử dụng để lựa chọn slave cần giao tiếp.

Ngoài ra, chân MOSI còn có các tên khác:

- SIMO, MTSR: trên cả thiết bị master và slave

- SDI, DI, DIN, SI: trên thiết bị slave

- SDO, DO, DOUT, SO: trên thiết bị master

Chân MISO còn có các tên khác:

- SOMI, MRST: trên cả thiết bị master và slave

- SDO, DO, DOUT, SO: trên thiết bị slave

- SDI, DI, DIN, SI: trên thiết bị master

Trong các thiết bị chỉ hoạt động ở chế độ slave, chân MOSI còn có tên SDI (Serial Data In) và MISO còn có tên SDO (Serial Data Out).

Chân Slave Select còn có các tên khác:

- SS, SS, SSEL, nSS, /SS, SS# (slave select)

- CS, CS (chip select)

- CSN (chip select/enable)

- CE (chip enable)

Hoạt động[sửa | sửa mã nguồn]

Bus SPI hoạt động với một master với một hoặc nhiều slave.

Nếu một slave được master chọn để giao tiếp, chân SS khi đó sẽ được ghi mức LOW nếu slave này cho phép giao tiếp với master. Một số slave yêu cầu tín hiệu xung xuống ở chân SS để khởi tạo một kết nối master-slave, ví dụ như Maxim MAX1242 ADC, khi yêu cầu tín hiệu HIGH -> LOW. Với nhiều slave trên đường truyền SPI, mỗi slave này sẽ yêu cầu một chân SS tương ứng ở master cho quá trình giao tiếp.

Truyền dữ liệu[sửa | sửa mã nguồn]

Để bắt đầu quá trình truyền dữ liệu, master sẽ cấu hình xung clock để tương ứng với tần số hỗ trợ bởi slave, thường lên đến vài MHz. Master sau đó lựa chọn slave cần giao tiếp với chân SS tương ứng và ghi giá trị 0 lên chân này. Nếu có yêu cầu chờ trên đường truyền, ví dụ như quá trình chuyển đổi ADC đang diễn ra, master sẽ phải chờ trong khoảng thời gian đó trước khi khởi tạo xung clock.

Quá trình truyền dữ liệu song công diễn ra trên mỗi chu kỳ xung clock SPI. Master truyền một bit trên đường dây MOSI, và slave nhận bit này; cùng lúc đó, slave truyền một bit trên đường dây MISO và master nhận bit này. Quá trình này diễn ra kể cả khi master và slave chỉ cần thực thi truyền thông theo một chiều, ví dụ như master chỉ cần gởi data đến slave.

Quá trình truyền thường bao gồm 2 thanh ghi dịch với kích thước cố định, ví dụ như 8 bit, một thanh ghi dịch cho master và một thanh ghi dịch cho slave. Một cách trừu tượng, hai thanh ghi này được kết nối theo kiểu vòng. Khi đó, quá trình truyền sẽ bao gồm các bước:

Bước 1: Chân SS với slave tương ứng mà master muốn truyền/nhận sẽ được master ghi mức logic thấp

Bước 2: Bit MSB sẽ được truyền đi trước. Trong một xung clock, cả master và slave đều dịch ra 1 bit và đưa bit này đến bên slave hoặc master cần truyền tương ứng. Trong xung clock tiếp theo, ở mỗi bên nhận, bit được lấy mẫu trên đường truyền và được lưu như là bit LSB mới nhất trên thanh ghi dịch. Sau khi các bit trên thanh ghi dịch được đẩy ra hoặc đã nhận vào toàn bộ, cả master và slave đã hoàn tất việc trao đổi giá trị thanh ghi. Nếu nhiều data hơn cần được truyền đi, các thanh ghi dịch sẽ được load lại và quá trình trên được lặp lại.

Bước 3: Khi hoàn tất, master ngừng việc đảo xung clock và ngừng chọn chân SS với slave tương ứng. Khi đó chân SS sẽ được master ghi mức logic cao.

Việc truyền SPI thường là việc truyền 8 bit. Tuy nhiên cũng có các trường hợp mà nhiều hơn 8 bit được truyền đi, ví dụ như truyền 16 bit trong các bộ điều khiển màn hình cảm ứng hay các bộ giải mã tín hiệu âm thanh, như IC TSC2101 của Texas Instruments, hay truyến 12 bit với các bộ chuyển đổi DAC hoặc ADC.

Clock polarity và phase[sửa | sửa mã nguồn]

Bên cạnh việc thiết lập tần số xung clock, SPI master còn phải cấu hình clock polarity (tạm dịch: cực của xung clock) và clock phase theo data. Tài liệu chính thức Motorola SPI Block Guide đặt tên 2 khái niệm này theo thứ tự là CPOL và CPHA (clock polarity và phase). 2 khái niệm này được dùng cho cả master và slave. Biểu đồ thời gian bên cạnh thể hiện CPOL và CPHA.

CPOL được xác định dựa trên xung SCK với:

- CPOL = 0 khi xung dẫn đầu của 1 chu kỳ là xung cạnh lênh, xung còn lại là xung cạnh xuống.

- CPOL = 1 khi xung dẫn đầu của 1 chu kỳ là xung cạnh xuống, xung còn lại là xung cạnh lên.

Giá trị của CPOL có thể được đảo lại bởi cổng NOT logic.

CPHA dựa trên việc định thời điểm (tức là phase) của dữ liệu bit tương ứng xung clock.

- CPHA = 0 khi bit dữ liệu đầu ra đúng với xung SCK còn lại còn xung dẫn đầu rơi vào khoảng giữa của bit dữ liệu.

- CPHA = 1 khi bit dữ liệu đầu ra đúng với xung SCK dẫn đầu còn xung còn lại rơi vào khoảng giữa của bit dữ liệu.

Từ đây, việc lựa chon các giá trị CPOL và CPHA sẽ tương ứng với 4 chế độ hoạt động trên SPI. 4 chế độ này được quy ước trên tất cả các dòng vi điều khiển có hỗ trợ SPI:

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

Chế độ SPI cũng thường được quy ước theo dạng tuple cho (CPOL, CPHA), ví dụ (0, 1) để chỉ CPOL=0 và CPHA=1.

Để truyền thông SPI thành công, cả master và slave phải có cùng chế độ (CPOL, CPHA). Việc lựa chọn 4 chế độ (CPOL, CPHA) không ảnh hưởng đến hiệu suất truyền SPI.

Kết nối từng slave độc lập[sửa | sửa mã nguồn]

Mô hình phổ biến nhất của một bus SPI bao gồm một master kết nối với một hoặc nhiều slave, với các chân SCK, MOSI và MISO được nối đến tất cả các slave trên bus, mỗi slave sẽ kết nối đến một chân CS riêng trên master. Mỗi chân CS khi đó nên có một điện trở kéo lên để đảm bảo rằng chân CS đó luôn có mức logic xác định. Khi khởi tạo một giao tiếp SPI và một chân CS ứng với một slave được chọn. điện trở kéo lên này giúp ngăn chặn các chân CS của các slave phản hồi với master dù không được yêu cầu từ master này.[5]

Kết nối daisy chain[sửa | sửa mã nguồn]

Một số thiết bị triển khai SPI theo mô hình daisy chain, với chân MISO của slave đầu tiên được nối vào chân MOSI của slave thứ 2, và cứ thế tiếp tục như ở hình bên. Việc triển khai SPI trên mỗi slave khi đó cần phải đảm bảo rằng mỗi slave đó phải truyền đi được chính xác dữ liệu mà nó nhận được từ slave trước nó trong mỗi xung clock. Quá trình nhận và truyền dữ liệu đi trên các slave của bus SPI daisy chain sẽ kết thúc khi một chân/dây SS duy nhất trên bên được master ghi mức logic cao (chuyển từ logic thấp lên cao). Từ đó, mô hình SPI daisy chain chỉ sử dụng 1 chân SS trên đường truyền.[6]

Tài liệu tham khảo[sửa | sửa mã nguồn]

- NXP (2004). SPI Block Guide V04.01 (PDF). NXP. Bản gốc (PDF) lưu trữ ngày 29 tháng 10 năm 2021. Truy cập ngày 14 tháng 10 năm 2021.

Chú thích[sửa | sửa mã nguồn]

- ^ NXP 2004, tr. 13, "1.1 Overview"

- ^ “Extending the SPI bus for long-distance communication” (PDF). Truy cập ngày 14 tháng 10 năm 2021" ... designed for short-distance communication between integrated circuits."Quản lý CS1: postscript (liên kết)

- ^ “What is Serial Synchronous Interface (SSI)?”. Truy cập ngày 8 tháng 12 năm 2019.

- ^ NXP 2004, tr. 15, "2.2 Detailed Signal Description"

- ^ “Better SPI Bus Design in 3 Steps”. pjrc. Truy cập ngày 10 tháng 11 năm 2021.

- ^ “How to Daisy-Chain SPI Devices”. Truy cập ngày 7 tháng 10 năm 2022.

Liên kết ngoài[sửa | sửa mã nguồn]

- Giao tiếp SPI (tài liệu tiếng Nga)

- Дедюхин А.А. (25 tháng 6 năm 2007). “Декодирование и анализ сигналов шин I2C, SPI, RS-232C, RS-422, RS-485 и UART с использованием осциллографов LeCroy”. prist.ru (bằng tiếng Nga). Truy cập ngày 5 tháng 7 năm 2023.